# Experimental study on SEU mitigation in a commercial-off-the-shelf SRAM FPGA for the LHC Phase-2 upgrade

Charles Detemmerman

Master thesis submitted under the supervision of Prof. Frédéric Robert

The co-supervision of Prof. Gilles De Lentdecker

In order to be awarded the Master's Degree in Electrical Engineering

Academic year 2018-2019

# Abstract

Future upgrades to the Large Hadron Collider will lead to an increase in the levels of background radiation experienced by the detector electronics. Within the muon detectors of the Compact Muon Solenoid (CMS) experiment, a series of new components will be installed, including the GE2/1 and ME0 detectors. Inside their data acquisition chain is the subject of this thesis, the OptoHybrid. It is a board centred around an SRAM-based Field-Programmable Gate Array (FPGA), a type of programmable electronics which is highly susceptible to radiation-induced soft errors called single event upsets (SEU). These are non-damaging but they will modify the internal configuration of the FPGA, and cause errors in its output and internal signals. The FPGA model used in the OptoHybrid is the 28nm Xilinx Artix-7, which is not radiation-proof by nature. It must therefore be qualified for use in the CMS environment.

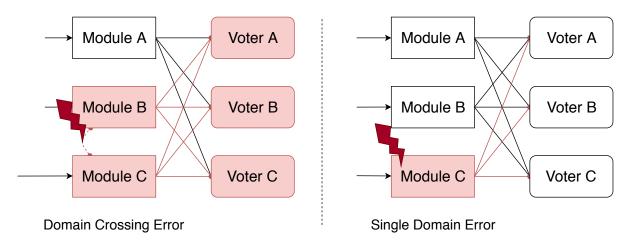

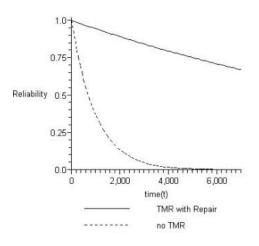

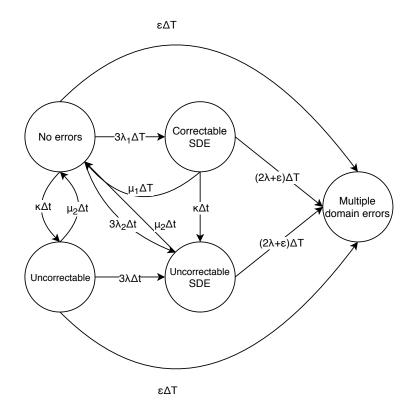

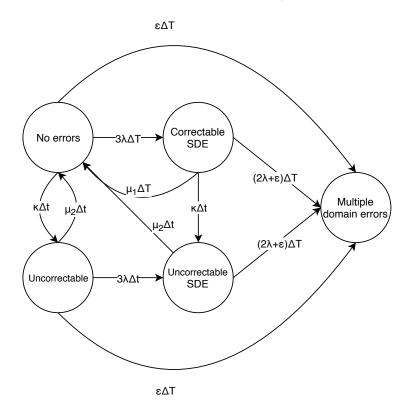

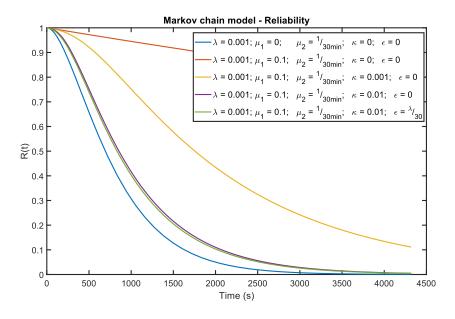

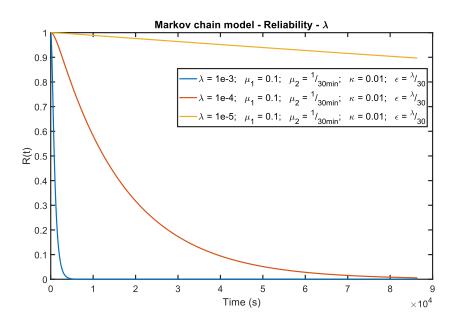

This thesis studies the possible systems which can be implemented to mitigate the effects of SEUs on the OptoHybrid. The selected system is a combination of configuration memory scrubbing using an Error Correction Code built into the Xilinx FPGA, and Triple Modular Redundancy. There are two main limitations to this system, the first is that the scrubber cannot repair memory frames which contain more than one erroneous bit. The second is that Triple Modular Redundancy breaks if more than one of the triplicated module is compromised. This can occur when SEUs accumulate, or when a single SEU flips multiple bits in the configuration memory. Because of these limitations, a reliability model based on Markov chains is proposed to predict the mean time to failure of the system.

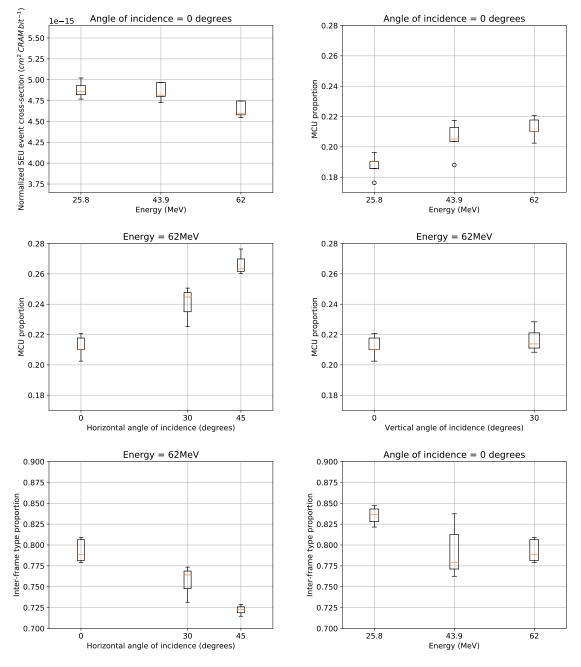

The second contribution of this thesis is a study into the impact of radiation on the FPGA through accelerated radiation testing at the UCLouvain's cyclotron facility. The main sources of SEUs in the CMS environment are neutrons. The UCLouvain's proton line is used as a neutron analogue as both have a similar SEU cross-section. The experimental protocols for two tests are presented, the first provides proton SEU cross-section data, and statistical data on the proportion of multiple cell upsets (MCU) for a range of energies present in CMS, and for a range of particle angles of incidence. The second studies the efficiency of the mitigation system, specifically it tests various TMR implementation, and measures parameters for the Markov chain model on the experimental firmware, which does not use modules from the OptoHybrid firmware.

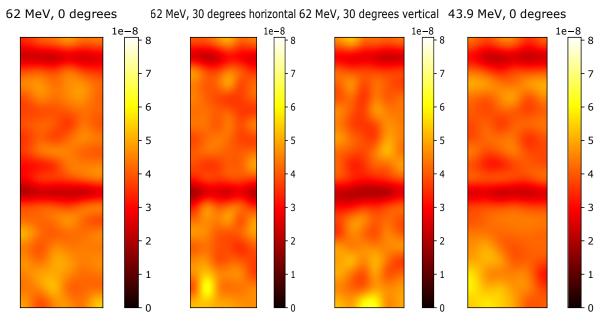

Previous work on the OptoHybrid of the GE1/1 detector, which used a 40nm Xilinx Virtex-6 FPGA, found a linear relation between proton cross-section and energy in the 30 to 62 MeV range, and a drop at 20 MeV. In the Artix-7 test, the proton cross-section is found to be lower but uniform in the 28.9 to 62 MeV range. Furthermore, the MCU proportion is found to rise both with energy and angle of incidence, as does the subset proportion of non-repairable MCUs.

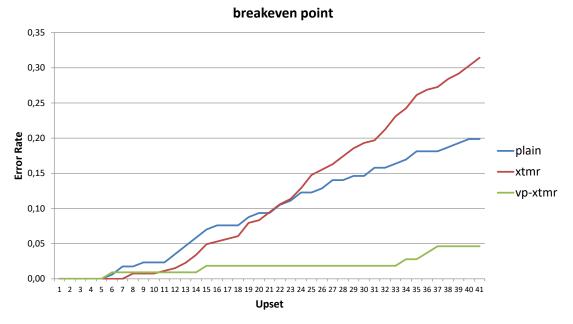

The mitigation system tests found that increasing the logical granularity of TMR yields significant improvement in error rates, while simulations with the Markov chain model indicate that the rate of non-repairable errors has a major impact on reliability. These results are only valid for the experimental firmware, therefore methods are proposed for measuring the Markov model parameters on the OptoHybrid firmware in the future.

Keywords: CMS, SRAM, FPGA, SEU mitigation, SEU cross-section, reliability modelling.

Student: Charles Detemmerman

**Degree:** Master of Science in Electrical Engineering

Academic year: 2018-2019

**Title:** Experimental study on SEU mitigation in a commercial-off-the-shelf SRAM FPGA for the LHC Phase-2 upgrade

# Acknowledgements

I would like to extend my thanks to my two supervisors, Prof. Frédéric Robert and Prof. Gilles De Lentdecker for their help and guidance throughout this master thesis. I must also express my deepest gratitude to Laurent Pétré for his involvement. The time and energy he has spent helping me during the course of this year has been truly invaluable.

To all my friends at the ULB and the VUB, I will say that you have made my time at university one of the most joyous experience of my life, it would not have been the same without you.

To my parents, thank you for your continuous support, love, encouragement, and everything else. To my brothers, you are certainly not the worst people I have ever met.

I thank you all.

It is an experience common to all men to find that, on any special occasion, such as the production of a magical effect for the first time in public, everything that can go wrong will go wrong.

Whether we must attribute this to the malignity of matter or to the total depravity of inanimate things, whether the exciting cause is hurry, worry, or what not, the fact remains.

Nevil Maskelyne

# Contents

| A        | bstra           | $\mathbf{ct}$  |                                                      | iii          |

|----------|-----------------|----------------|------------------------------------------------------|--------------|

| A        | cknov           | wledge         | ments                                                | $\mathbf{v}$ |

| In       | $\mathbf{trod}$ | uction         |                                                      | 1            |

| 1        | Con             | ntext          |                                                      | 3            |

|          | 1.1             | Large          | Hadron Collider                                      | 3            |

|          | 1.2             | Compa          | act Muon Solenoid                                    | 3            |

|          |                 | 1.2.1          | Overview of the Muon detectors                       | 6            |

|          |                 | 1.2.2          | Trigger system                                       | 6            |

|          | 1.3             | GEM            | detectors                                            | 8            |

|          |                 | 1.3.1          | Data acquisition system                              | 8            |

| <b>2</b> | Rad             | liation        | effects in FPGAs                                     | 15           |

|          | 2.1             | Basics         | of FPGAs                                             | 15           |

|          | 2.2             | Radiat         | tion characteristics                                 | 15           |

|          | 2.3             | Accum          | nulated effects                                      | 18           |

|          |                 | 2.3.1          | Displacement effect                                  | 18           |

|          |                 | 2.3.2          | Charge accumulation effect                           | 18           |

|          |                 | 2.3.3          | Total Ionizing Dose                                  | 18           |

|          | 2.4             | Single         | Event Effects                                        | 18           |

|          |                 | 2.4.1          | Origin                                               | 18           |

|          |                 | 2.4.2          | Categorization                                       | 19           |

|          | 2.5             | CMS I          | Environment                                          | 22           |

|          | 2.6             | Existin        | ng studies                                           | 24           |

|          |                 | 2.6.1          | Scaling trends                                       | 27           |

| 3        | SEU             | J <b>mitig</b> | gation techniques                                    | 29           |

|          | 3.1             | Radiat         | tion hardening solutions                             | 29           |

|          | 3.2             | Scrubb         | ping architectures                                   | 31           |

|          |                 | 3.2.1          | Blind scrubbing                                      | 31           |

|          |                 | 3.2.2          | Readback scrubbing                                   | 31           |

|          |                 | 3.2.3          | Hybrid schemes                                       | 32           |

|          |                 | 3.2.4          | External solutions                                   | 32           |

|          |                 | 3.2.5          | Xilinx Soft Error Mitigation solution                | 32           |

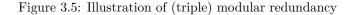

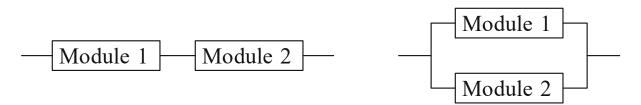

|          | 3.3             | Modul          | lar redundancy                                       | 34           |

|          |                 | 3.3.1          | N-modular redundancy                                 | 34           |

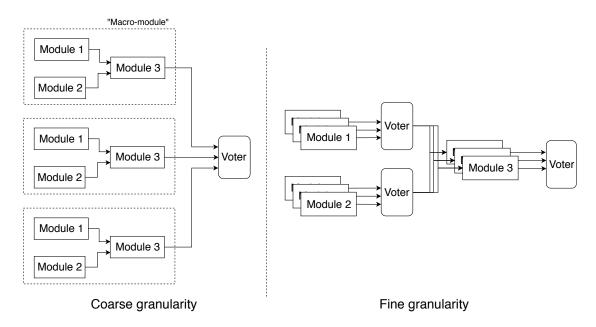

|          |                 | 3.3.2          | Granularity                                          | 35           |

|          |                 | 3.3.3          | Signal triplication and TMR logical areas            | 35           |

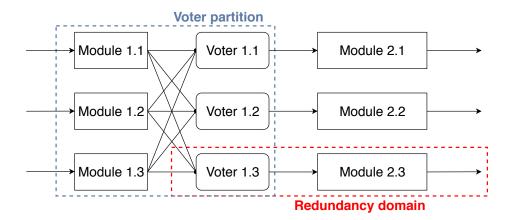

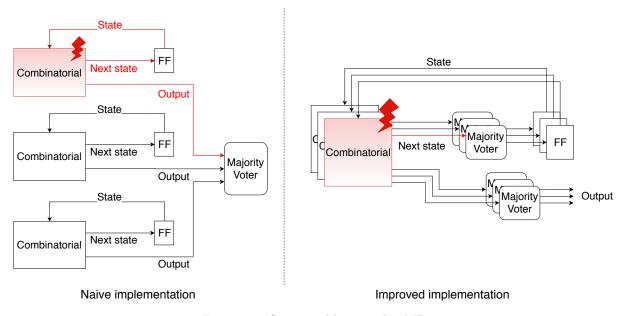

|          |                 | 3.3.4          | Sequential logic                                     | 36           |

|          |                 | 3.3.5          | Implementation                                       | 36           |

|          | 3.4             | Design         | ning a mitigation solution                           | 39           |

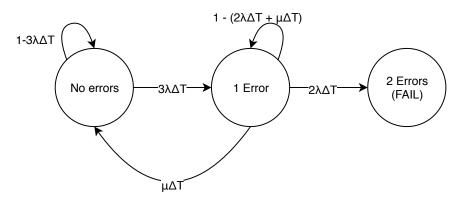

|          | 3.5             | System         | n reliability                                        | 39           |

|          |                 | 3.5.1          | Limitations of the mitigation solution               | 39           |

|          |                 | 3.5.2          | Notions of reliability theory for electronic systems | 40           |

|          |                 | 3.5.3          | Simple reliability model                             | 41           |

|                         |                                        | 3.5.4                                                                                                             | Markov chain model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                                            |  |  |  |

|-------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| 4                       | Exp<br>4.1<br>4.2                      | SEU c<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                                         | nts         testing campaign         ross-section test         Motivation         Principle         Experimental architecture         Parameters         Motivation         Motivation         Parameters         Motivation         Principle         Experimental architecture         Motivation         Principle         Principle         Parameters         Parameters         Parameters         Parameters         Principle         Principle         Principle         Parameters         Principle         Parameters         Parameters         Parameters         Parameters         Parameters         Parameters         Parameters         Parameters | <b>45</b><br>45<br>45<br>46<br>46<br>48<br>48<br>48<br>49<br>49<br>51                         |  |  |  |

| 5                       | <b>Dat</b><br>5.1<br>5.2<br>5.3<br>5.4 | a anal<br>SEU c<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>TMR<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Curren | ysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>53</b><br>53<br>55<br>55<br>55<br>55<br>55<br>58<br>58<br>58<br>58<br>59<br>62<br>63<br>63 |  |  |  |

| Co                      | onclu                                  | sion                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                                                            |  |  |  |

| Gl                      | ossai                                  | ry                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67                                                                                            |  |  |  |

| Bi                      | Bibliography                           |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |  |  |  |

| A Device specifications |                                        |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |  |  |  |

| в                       | Exp                                    | erime                                                                                                             | ntal dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                            |  |  |  |

| $\mathbf{C}$            | тм                                     | R Mo                                                                                                              | dule - VHDL Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                                                            |  |  |  |

| D                       | Mar                                    | rkov cl                                                                                                           | nain model solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81                                                                                            |  |  |  |

# Introduction

The Large Hadron Collider (LHC), developed in Switzerland by the European Organization for Nuclear Research (CERN) is, at almost 27 km in circumference, the most powerful particle collider ever built, and the largest machine in the world. A massive feat of physics and engineering, it currently involves thousands of researchers, technicians, engineers, and administrators across Europe and the world. In 2012, after four years in operation, the LHC has provided conclusive evidence for the existence of the Brout-Englert-Higgs boson, earning a Nobel Prize to François Englert and Peter Higgs. The first proton-proton collisions were achieved in 2010 at a total collisional energy of 7 TeV, steadily increased up to the present world record at 13 TeV.

Upgrades are now underway for Phase-2 of the LHC roadmap, during which the number of particles interactions in the detectors will increase by a factor of 10. Among the LHC detectors is the Compact Muon Solenoid (CMS) experiment in which, as part of the upgrades, new components will be installed, including the GE2/1 et ME0 detectors (GEM detectors) which are the subject of this thesis.

Among the electronic systems of the GEM detectors is the OptoHybrid board, a part of the data acquisition chain based around a Field-Programmable Gate Array (FPGA), the Xilinx Artix-7. FPGAs are programmable electronic devices, which can implement any sort of circuit based on a design they keep in memory (the firmware). When working in an environment of intensive ionizing radiation, FPGAs will tend to malfunction, and could even be damaged if the absorbed dose is high enough. This is due to the interactions the incident particles have with the semiconductor material of the electronic system. FPGAs which store their configuration in Static Random-Access Memory (SRAM) cells, such as the Artix-7, are particularly vulnerable as these cells can be upset, and the programmed circuit can therefore be modified. In the context of CMS the main consequence of radiation will be Single Event Effects (SEE), a collection of disruptive effects created by the interaction of a single particle with the FPGA, but which are most often reversible. These SEEs will be caused mainly by neutron radiation; insuring that the FPGA is protected against them is essential to the viability of the OptoHybrid board in CMS operation.

Simulations have shown that the background neutron radiation in the CMS cavern will increase significantly during Phase-2. This will make the electronic systems, and in particular the FPGAs, more prone to errors. The main contribution of this thesis is first to provide experimental data on the interaction cross-section of neutron particles with the Artix-7 FPGA, as well as statistical data on the rate of Multiple Cell Upsets (MCU). MCUs are the consequence of an SEE creating multiple bit flips in SRAM cells, which is particularly problematic in the context of SEE mitigation for reasons which will be presented in Chapter 3. Previous work on this subject has been done for the GE1/1 detector [29] [28], which also contained an OptoHybrid board, but based around an older FPGA model, the Xilinx Virtex-6. As the Artix-7 is based around a new 28nm technology node, and considering that the ME0 detector will experience a neutron flux ten times higher than the GE1/1, the interaction of the Artix-7 with the radiation environment of CMS must also be assessed.

The second contribution of this thesis will be an investigation into the efficiency of the mitigation solution currently being considered for the OH FPGA. Because the mitigation solution is limited in capability, a model is proposed to predict its reliability over time. Exact predictions are not given for the reliability of the OptoHybrid as its firmware could not be used for the experiment, instead data gathered from an experimental firmware is applied to the reliability model in order to give a sense of where the bottlenecks are. Indications are also given on how to do the same for the OptoHybrid firmware.

This master thesis investigates the causes and consequences of radiation effects in FPGAs (Chapter 2), and proposes potential mitigation solutions (Chapter 3). An experimental protocol is designed for testing the interaction between the FPGA and a proton beam, and for testing the efficiency of the mitigation system (Chapter 4). The results of irradiation tests carried out during the thesis at the UCLouvain's cyclotron facility are then analysed and presented (Chapter 5).

# Chapter 1

# Context

### 1.1 Large Hadron Collider

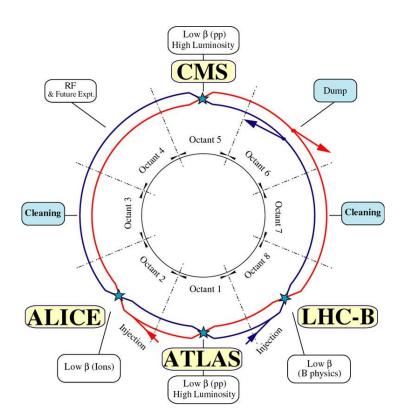

The Large Hadron Collider (LHC) at CERN is the world's largest and most powerful particle accelerator. It consists of a 27-kilometre ring of superconducting electromagnets, along which are spaced several accelerating structures to boost the energy of the particles. Inside the vacuum of the accelerator, high energy particle beams travel at close to the speed of light in both directions around the ring, and collide at four particle detectors: ATLAS, CMS, ALICE and LHCb (Figure 1.1) [49]. The Compact Muon Solenoid (CMS) is of particular interest, as this work is directly intended to help its upgrade to the future high-luminosity phase.

### Luminosity and Phase-2

In accelerator physics, luminosity L is defined as the proportionality factor between the number of events (collisions) per second  $\frac{dN_c}{dt}$  and the interaction cross section  $\sigma_p$  (the area transverse to their motion within which the particles must meet for a collision to occur, the unit is cm<sup>2</sup>) [20].

$$\frac{dN_c}{dt} = L \cdot \sigma_p$$

The unit of luminosity is therefore  $\text{cm}^{-2} \text{s}^{-1}$ . A related quantity is the *integrated luminosity*, which is the integral of the luminosity with respect to time, usually expressed in *inverse femtobarn* ( $fb^{-1} = 10^{39} \text{ cm}^{-2}$ ).

$$L_{int} = \int L \cdot dt$$

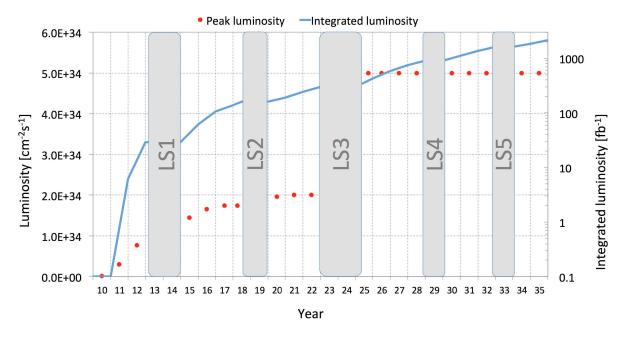

During the lifetime of the LHC, the luminosity of the accelerator will steadily increase from a current integrated luminosity of  $300 \text{ fb}^{-1}$  to a target of  $3000 \text{ fb}^{-1}$  in the upcoming upgrade, the High-Luminosity LHC (HL-LHC). The activity of the LHC is separated into periods of data acquisition and periods of *long shutdowns* (LS), during which repairs and upgrades are undertook. As can be seen in Figure 1.2, we are currently in the second Long Shutdown (LS2), in which installations for the HL-LHC have already started. The current "Phase-1" of LHC operation will continue until the year 2023, when the LS3 will finalize the HL-LHC upgrade. If all goes well, this "Phase-2" of LHC operation will start in 2026. This increase in luminosity will mean increased stress on the system at several levels. Increased data rates on the one hand will require improvements in the data acquisition chain but, more significantly for this thesis, it will also mean higher background radiation levels, which will increase the risk of failure in electronics.

### 1.2 Compact Muon Solenoid

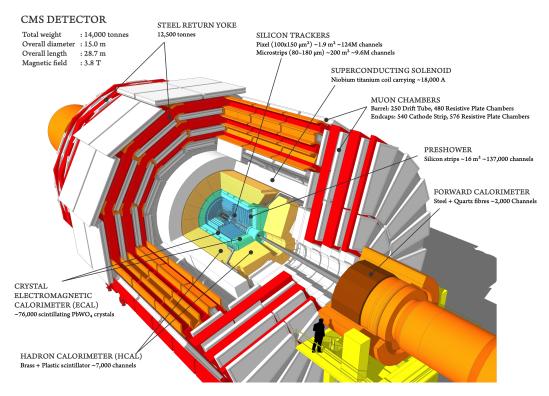

The CMS is a general purpose detector, built around a huge solenoid magnet generating a field of 4 tesla, almost 100,000 times the magnetic field of the Earth. It has a cylindrical shape, 28.7 m long and 15 m in diameter [28]. The detector is separated into two areas: the *barrel*, forming the cylinder, and two *endcap* regions, closing it off at both ends (Figure 1.3). The detector contains subsystems designed to measure the energy and momentum of photons, electrons, muons and other products of the collisions.

Figure 1.1: Schematic of the LHC [6]

Figure 1.2: LHC luminosity evolution [17]

Figure 1.3: Cutaway diagram of the CMS detector [41]

At the center of the CMS, particles will collide, generating a shower of secondary particles, which will again generate more particles through interactions with material in the detector. Some of these particles' trajectories will go through the electronic equipment of the detector, and potentially disrupt their normal behaviour. As can be seen on Figure 1.3, there are several layers forming the detector, which will be briefly detailed in the following section, followed by a discussion of the CMS triggering system.

### CMS layers

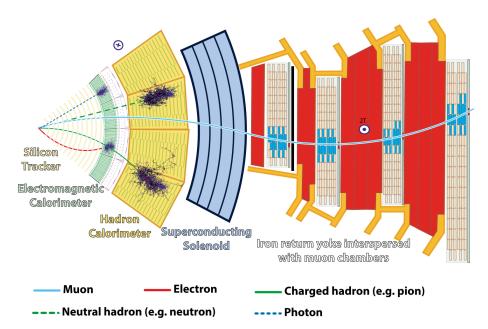

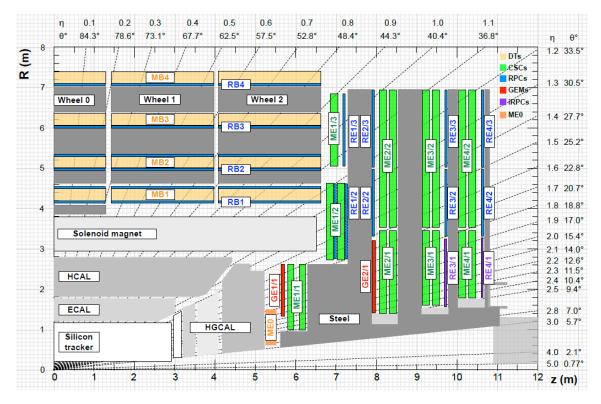

Figure 1.4 provides a more detailed view of the CMS barrel, on which one can identify six regions: the interaction point, the tracker, the Electromagnetic Calorimeter (ECAL), the Hadronic Calorimeter (HCAL), the superconducting magnet and the muon detector, interleaved with a steel return yoke used to guide the magnetic field. The arrangement is similar for the endcap regions.

The **silicon tracker** is used to determine the collision point and the momentum of charged particles. It can reconstruct the paths of high-energy muons, electrons and hadrons, as well as see tracks coming from the decay of very short-lived particles such as beauty or "b quarks". The pervasive magnetic field will bend the path of charged particles, enabling momentum detection. The pixels, at the very core of the detector and dealing with the highest intensity of particles, and the silicon microstrip detectors that surround it are made entirely of silicon. As particles travel through the tracker the pixels and microstrips produce tiny electric signals that are amplified and detected [11].

The **ECAL** consists of tungstate crystals, a highly transparent material producing light when electrons or photons pass through it. Photodetectors are placed on the back in order to convert and record the produced light by converting it to electrical signals. A calorimeter's purpose is to detect the energy of the incident particles, which it does by allowing these particles to interact within the calorimeter and deposit their energy. The amount of interaction with the detector is measured and the energy is derived from it.

Another type of calorimeter in CMS is the **HCAL**, which is used to detect hadrons (particles made of quark and gluons), as the name suggests. It also provides indirect measurement of the presence of non-interacting, uncharged particles such as neutrinos. It is made up of alternating layers of "absorber" material, reducing the energy of the particle, and "scintillator" material which give short bursts of light when a particle passes through. By extrapolating the path of the particle from the scintillator data, one can compute the total energy exchanged between the particle and the absorbing material.

Figure 1.4: Cross-sectional slice of the CMS detector [4]

Muons and neutrinos are the only particles remaining after the solenoid due to their high penetration range (low interaction cross-section). Therefore the **muon detector** is placed there. [28]

### 1.2.1 Overview of the Muon detectors

#### CMS coordinate system

The schematic of Figure 1.5, which will be presented in the next section, is displayed in the CMS coordinate system. The origin is the nominal interaction point of the beams, the y-axis points upwards, the x-axis towards the center of the LHC loop, and the z-axis along the beam direction. The polar coordinates  $(r, \theta)$  are defined in the x-y plane, and the **pseudorapidity** is defined as follows:

$$\eta = -\ln(\tan(\frac{\theta}{2})) \tag{1.1}$$

### Detectors

The muon tracker is of particular interest as the target FGPA board of this thesis (the OptoHybrid) is part of the muon tracker data acquisition system. It is made up of three different detector types: Drift Tubes (DTs), Cathode Strip Chambers (CSCs), and Resistive Plate Chambers (RPCs), to which a new type will be added during Phase-2: the Gas Electron Multiplier (GEM). DTs and CSCs are placed in the barrel and the endcaps respectively, and RPCs are present in both regions. One quadrant of CMS is shown on Figure 1.5, highlighting the placement of the various technologies inside the detector. Three systems are to note on this diagram: GE1/1, GE2/1 and ME0. These are the three GEM-type detectors which will be added for Phase-2 [10].

The GE1/1 system is presented extensively in the PhD Thesis of Thomas Lenzi [29] and is currently being installed. We will focus on the GE2/1 and ME0 detectors, which are similar in design but use an updated version of the OptoHybrid board. The GE1/1 and GE2/1 systems cover the forward pseudorapidity range  $1.6 < \eta < 2.4$  and are mainly designed to improve the trigger system in this region (see Section 1.2.2). The ME0 detector will increase the tracker coverage up to  $\eta = 2.8$ . The radiation flux increases with pseudorapidity (see Section 2.5), which means the ME0 will see more radiation than the GE1/1 and GE2/1 systems.

### 1.2.2 Trigger system

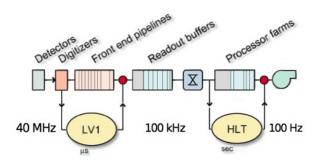

To maximize the number of interesting events for the LHC physics program, a very large amount of collisions per second is required. A single beam crossing produces around 1MB of data every 25ns

Figure 1.5: Cross-section of a CMS quadrant [10]

(40MHz crossing rate), which would result in 40 terabytes per second if all the sensor data was captured. Obviously this is not workable, therefore a *triggering system* is implemented. Whenever a trigger is generated, the full detector data is captured and stored. This allows a reduction in the data acquisition rate from 40MHz to 100kHz (500 kHz in Phase-2) (Level-1 trigger) and then to 1.5kHz (High-Level Trigger) [29].

The L1 trigger is made of custom electronics designed to quickly identify features of interest in the data, in order to discriminate between events. It must take a decision under 3.2 µs (12.5 µs in Phase-2) on whether to pass the data to the next trigger stage or not. At this stage, only the information from the HCAL, ECAL and muon chambers are used.

Figure 1.6: Block diagram of the trigger system pipeline [53]

If a collision passed the L1 trigger, all of the buffered data is sent through optical fibers to a computer farm, which will perform the High-Level Trigger (HLT). The lower event rate at this point allows time for a much more detailed analysis in software (mainly C++).

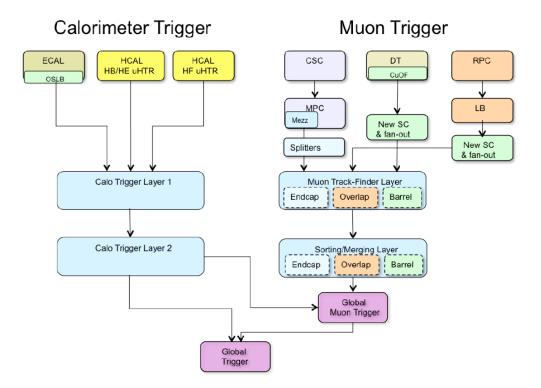

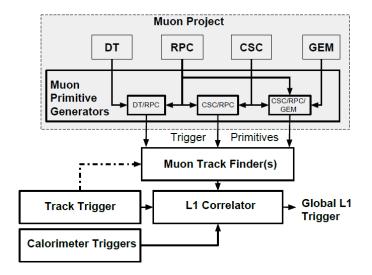

### Global L1 Trigger

Only the information from the HCAL, ECAL and muon chambers are used at the L1 Trigger stage. Under the current system this means data from the CSCs, DTs and RPCs (see Figure 1.7). With the Phase-2 upgrade, hits from the new GEM chambers will be combined at an early stage with data from

Figure 1.7: Global L1 trigger system [3]

the CSCs to improve efficiency (see Figure 1.8) [10].

The energy deposition data from the HCAL and ECAL is sent to the Calo Trigger Layer 1 which performs data formatting and concentration, and forwards events to the Calo Trigger Layer 2. Hits from the different muon detector chambers (barrel, endcap and overlap) are combined in the Muon Track-Finder layer, which extrapolates tracks from the data using pattern recognition algorithms. From then on, the sorting/merging layer selects the best event candidates, which are sent forward to the Global Muon Trigger (GMT). Further processing is done with the data from the calorimeters in the GMT and in the Global Trigger.

## **1.3 GEM detectors**

The main purpose for installing the GEM detectors is the improvement of the triggering system of CMS. Without it, the coming increases in instantaneous luminosity would degrade the performance of the system due to the rate limitation of the ME1/1 stations (see Figure 1.5).

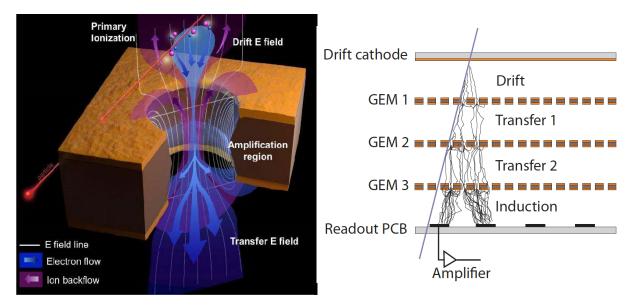

A GEM foil is a 50 µm-thick polymer foil, covered with 5 µm-thin copper sheets on both sides, and perforated at a high density by microscopic holes. When a high voltage is applied between the two layers of copper (typically on the order of 300V), field densities inside the holes reach approximately  $80 \text{ kV cm}^{-1}$ (see Figure 1.9 on the left). When a charged particle passes through the detector, the electrons released from the ionized gas in the chamber are accelerated towards the holes of the foil. These electrons will reach high kinetic energies inside the holes, and then ionize the medium themselves, producing an avalanche of secondary electrons, hence the name Gas Electron Multiplier. To achieve high gains, there are two solutions: increase the voltages on the foil or use multiple foils. When working with very high electric fields, discharges which can damage the detector are possible, the second option is therefore preferred. The choice was made to use three GEM foils, which is why they are called triple-GEM detectors (see Figure 1.9 on the right). [29]

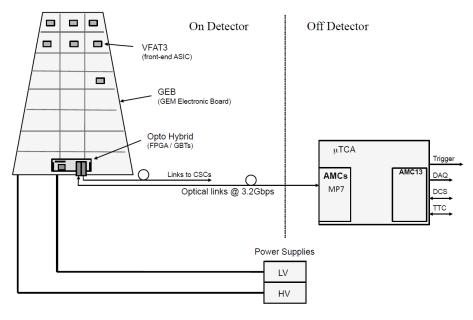

### 1.3.1 Data acquisition system

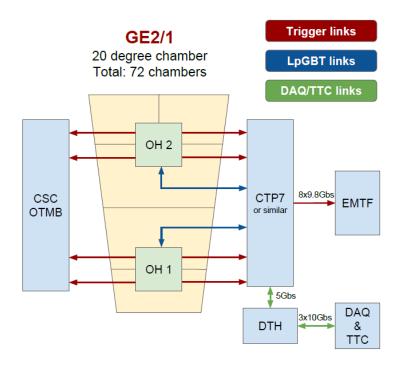

A generic block diagram of a triple-GEM chamber is shown on Figure 1.10. The diagram illustrates the main components for the readout of a single GEM chamber. A specific diagram for GE2/1 is shown on Figure 1.11, note the direct connections to the CSC used for the trigger system (see also Figure 1.8).

Figure 1.8: Upgraded L1 muon trigger [10]

Figure 1.9: Schematic of the field lines inside a GEM foil (left). Principle of operation of a triple-GEM chamber (right) [12]

Figure 1.10: Generic GEM readout system [12]

Figure 1.11: GE2/1 readout system [10]

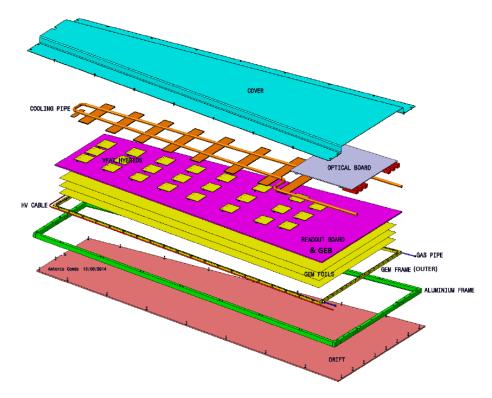

Figure 1.12: Exploded view of a single triple-GEM module [10]

### **GEM Electronics Board**

The GEM Electronics Board (GEB) is the host of the data acquisition electronics in the GEM (see Figure 1.12). It routes signals from the VFAT3 Application-Specific Integrated Circuit (ASIC) to the OptoHybrid (OH), provides power to the chips and electric shielding to the detector. The following sections will serve as a brief tour of the important components.

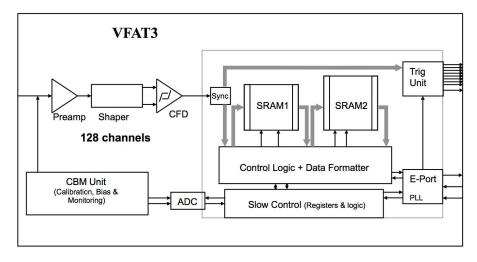

### VFAT3

The VFAT3 is the front-end data acquisition chip, optimized for gaseous detectors. Its function is to digitize the analog signals coming from the GEM foils and provide fast trigger and tracking data. The trigger data is sent over a fixed latency path to the L1 trigger system, while the tracking data holding the full granularity information of the events is stored in two Static Random-Access Memorys (SRAMs). If the L1 trigger algorithms decides to accept the event, the full tracking data will be sent over a variable latency path. It is comprised of an analog front-end, which does the signal shaping and digitization, and a digital back-end for control and readout (see Figure 1.13) [29].

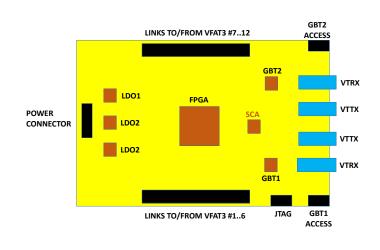

### OptoHybrid

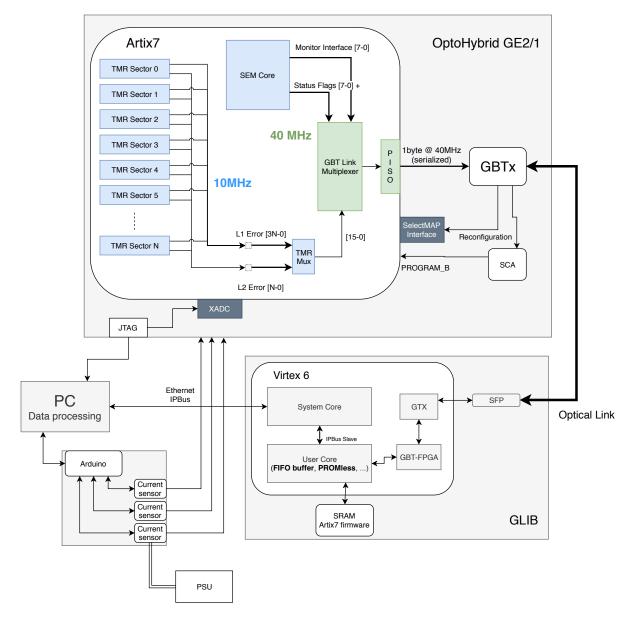

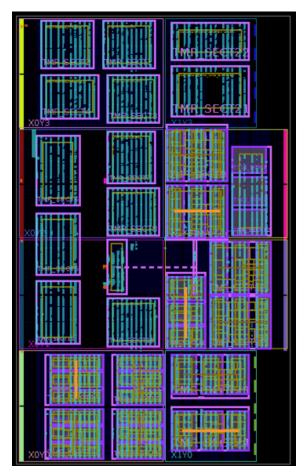

The OptoHybrid board is the interface between the VFAT3 and the off-detector system (see Figure 1.14). It is centred around an Field-Programmable Gate Array (FPGA) (a Xilinx Artix-7 in the GE2/1 OH, see Annex A.1 for the details) and Integrated Circuits (ICs) dedicated to the operation of the optical link. The FPGA applies zero suppression algorithms to the trigger data, formats it, and sends it forward to the CSCs and the GEM trigger system separately over two optical links [29]. A new version of the OH board has been developed for the GE2/1 and ME0, switching from a Xilinx Virtex-6 FPGA to an Artix-7 model. Because this FPGA, like the previous one, is not made to be resistant to radiation (radiation-hardened), studies have to be made to predict its behaviour in a high-radiation environment, and some systems must be developed to counteract the radiation effects and insure proper behaviour of the electronics. Previous studies have been made on the Virtex-6 [28] [29], however as the technology node for the Artix-7 as been shrunk to 28nm (40nm for the Virtex-6), the radiation performance must be re-evaluated.

Figure 1.13: Block diagram of the VFAT3 ASIC [12]

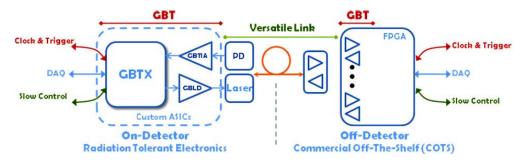

### $\mathbf{GBT}$

The GigaBit Transceiver (GBT) architecture is part of the "Radiation Hard Optical Link Project" developed by CERN, which aims at providing radiation hard tools for optical communication. The technology provides bidirectional 4.8 Gbps (Gigabits per second) serial communication, and is designed to connect on-detector electronics to the off-detector systems. It is used for data acquisition, timing, trigger and control. This architecture is implemented in two system: the GBTx rad-hard ASIC, which is on the OH board, and the GBT-FPGA, which is a module that can be implemented inside an FPGA. Figure 1.15 illustrates the optical link setup with these systems at both ends.

### **Back-end electronics**

The function of the back-end electronics is to: handle slow control requests for the detector subsystems, interpret Timing, Trigger and Control (TTC) signals, and readout the trigger and tracking data from the OHs. This is handled by the CTP7 (see Figure 1.11), a board in the Advanced Mezzanine Card format, equipped with a large Xilinx Virtex-7 FPGA for computational power and a Xilinx Zynq System on Chip (SoC) running a Linux operating system for monitoring [48].

Figure 1.14: Diagram and top view picture of the GE2/1 OptoHybrid board (Mikhail Matveev)

Figure 1.15: Architecture of a radiation hard optical link setup integrating the GBTx and GBT-FPGA [58]

# Chapter 2

# **Radiation effects in FPGAs**

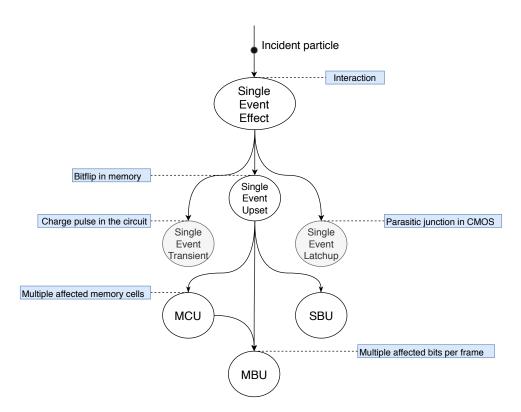

In FPGAs, radiation effects can be classified in two broad categories: accumulated effects (i.e. degradation mechanisms), and Single Event Effects (SEEs). The former is caused by the accumulation of particle interactions with the semiconductor, degrading its performance over time, up to a total device failure. The latter encompasses all instantaneous effects caused by a single particle, which will usually not permanently damage the device (with some exceptions), but which can cause errors in various ways. A non-exhaustive summary of single event effects is shown on Figure 2.1, the various categories will be presented in Section 2.4.2.

# 2.1 Basics of FPGAs

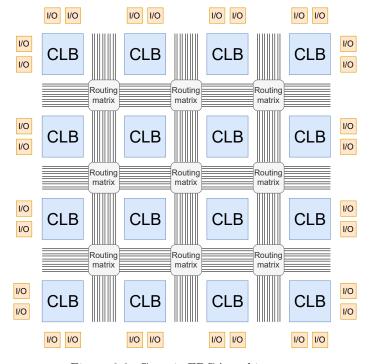

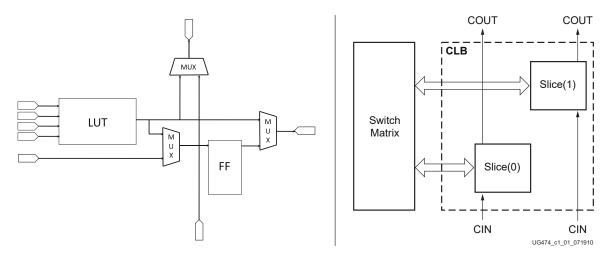

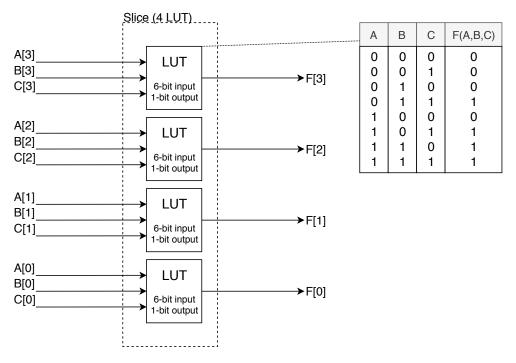

A generic FPGA architecture is shown on Figure 2.2, it consists of logic blocks (which we call here configurable logic block or **CLB**, according to the Xilinx terminology) interconnected through programmable **routing matrices** (also called switch matrices). The CLBs contain look-up tables (LUT) implementing combinatorial logic functions (truth tables), storage elements (flip-flops) for sequential logic and pipelines, multiplexers and carry logic [1]. A 7-series Xilinx FPGA follows this general architecture, and has a total of 8 LUTs per CLB (divided into two *logic slices* containing 4 LUTs each), see Figure 2.3.

The functionality of an FPGA is described in Hardware Description Languages (HDL) such as VHDL or Verilog. In a nutshell, the HDL functional description will be *synthesized* into digital logic and *implemented* into the FPGA by configuring the memory of the LUTs, connecting them together and to flip-flops within the CLBs through the various multiplexers, and between CLBs through the routing matrices.

The result of this implementation is the *firmware*, a complete description of how the FPGA should be configured. This firmware is then translated into a *bitstream*, a sequence of bits which can be loaded into the FPGA. Loading the bitstream can be done through various interfaces, JTAG being the most commonly used during development through a USB-JTAG adapter connected to a computer.

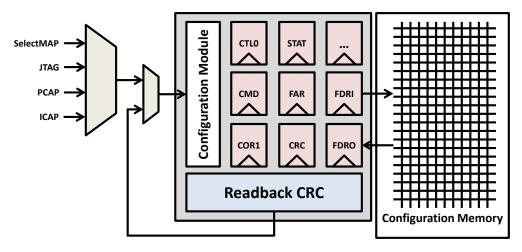

As FPGA are programmable electronic devices, their configuration is stored in what is called the **Configuration Memory** (or CRAM). This refers to all the distributed elements of memory which implement the design (e.g. LUT tables, routing matrix configuration, etc), and its content is (part of) the content of the bitstream. In a 7-series Xilinx FPGA, the bitstream (an by extension the CRAM) is arranged in *frames* of 101 *words* (32 bits per word). The most common type of FPGA is SRAM-based (i.e. the design is stored in volatile SRAM memory cells), but other types include flash-based (using non-volatile flash memory) and antifuse-based (can only be programmed once). The Artix-7 is an SRAM-based FPGA.

### 2.2 Radiation characteristics

Let us define some commonly used terms for radiation and its interaction with electronic devices:

The particle **flux** f is the number of particle p that crosses the area a in one unit of time t. It is measured in cm<sup>-2</sup> s<sup>-1</sup>, or equivalently in Hz cm<sup>-2</sup>.

$$f = \frac{p}{a \cdot t} \tag{2.1}$$

Figure 2.1: Summary of single event effects within an FPGA

Figure 2.2: Generic FPGA architecture

Figure 2.3: Generic configurable logic block with a single LUT (left). Xilinx CLB with two slices of 4 LUTs (right). [5]

Figure 2.4: Penetration of a particle in a material [5]

The particle **fluence**  $\Phi$  is the integral of the flux over time. It is measured in cm<sup>-2</sup>.

$$\Phi = \int_0^t f(t)dt \tag{2.2}$$

The **cross-section**  $\sigma$  is a characteristic area of the device that represents the tendency of incident particles to interact with the target. In the context of electronic devices, it is defined as in Eq. 2.3, with N being the total count of some sort of event in the device (e.g. SEU, SET, see Section 2.4). It can be conceived of as the equivalent area of the device if all particles going through it produced an event.

$$N = \sigma \cdot \Phi \tag{2.3}$$

The **linear energy transfer** (LET) is a measure of the amount of energy per unit length transferred by an ionizing particle to an incident material [15]. It concerns only energy transferred by ionization, and in this it differs from the stopping power, which includes the nuclear collisions. One speaks of the restricted LET when it is focused on the energy transferred to the material in a vicinity of the track (See Figure 2.4) by means of secondary electrons with  $E \leq \Delta$  emitted during the interactions ( $\Delta$  being the energy required to leave the cylinder described in Figure 2.4). Indeed, higher energy electrons will travel further away into the material and will not affect the semiconductor along the track of the particle. The restricted LET is defined in Eq. 2.4, where  $dE_{\Delta}$  is the energy lost by the particle while travelling a distance ds. The unrestricted LET is given by  $\lim_{\Delta\to\infty} LET_{\Delta}$ . When studying the effects of radiation on electronic devices, LET is usually expressed in MeV cm<sup>2</sup> mg<sup>-1</sup>, which is the standard definition of LET (MeV cm<sup>-1</sup>) divided by the material density.[5]

$$LET_{\Delta} = \frac{-dE_{\Delta}}{ds} \tag{2.4}$$

### 2.3 Accumulated effects

### 2.3.1 Displacement effect

When a heavy particle enters the semiconductor, it will be scattered by collisions with the nuclei of the material, dislocating atoms and creating point defects in the crystal lattice. The more energy is transferred from the particle to the material, the more the dislocations. These point defects are recombination centers for charge carriers in the material (so-called "carrier traps"), which will worsen the analog properties of the semiconductor. Such damage can be repaired by heating the device, providing energy to the lattice to repair itself (annealing). This effect is mostly caused by neutrons, protons, alpha particles, heavy ions and very high energy gamma photons [5].

### 2.3.2 Charge accumulation effect

Ionization is a mechanism by which charge is released within the material traversed by the particle. This can occur in two ways, through *direct* or *indirect* ionization. Direct ionization is caused by charged particles, such as heavy ions, electrons or positrons. When these particles enter the material, they can tear electrons away from neutral atoms, or give electrons to ionized atoms, provoking a movement of charge along the particle's path. Indirect ionization is caused by neutral particles, such as neutrons or photons, which can ionize the atoms within the crystal lattice through collisions, creating electron-hole pairs [5].

Charge accumulation is a consequence of both ionization and displacement effects. Charge within the semiconductor can become trapped in lattice dislocations, or in the insulation oxides around and within the transistor's structure. In particular, charge trapped near the gate oxide will create a permanent gate bias, influencing the transistor threshold voltage. This effect will lead to a gradual degradation of performance, up to a total loss of functionality when a transistor becomes permanently open (or closed) [10] [5].

### 2.3.3 Total Ionizing Dose

The Total Ionizing Dose (TID) is a measure of the total energy released into the material by ionizing radiation. Its SI unit is the Gray  $(1 \text{ Gy} = 1 \text{ J kg}^{-1})$  but it is often measured in rad (1 rad = 0.01 Gy) [35]. It depends on exposure time, the flux of particles, and their LET. TID models the effects of charge accumulation as well as displacement damages, it is therefore associated to a global worsening in performance. Another effect of TID is a change in SEE sensitiveness, one consequence of which is that SEUs which would cause reversible *bit-flips* in memory elements (see Section 2.4.2) could cause so-called *stuck bits*, whose correct value cannot be restored. TID effects can usually be repaired through annealing [5].

### 2.4 Single Event Effects

Single event effects are the category of effects directly caused by an incident particle. They can be transient or permanent, repairable (*soft error*) or not (*hard error*) depending on the area affected. Among the soft error category are single event upsets (SEU), single event transients (SET) and single event functional interrupts (SEFI). This type of error can typically be repaired by reloading the FPGA firmware, or by cycling the power. One example of a hard error is the single event latch-up (SEL), which can cause permanent damage to the electronics. All of these will be presented in the following sections. [10]

### 2.4.1 Origin

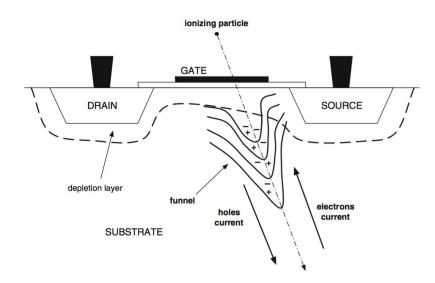

An ionizing particle penetrating into a semiconductor device through its depletion layer will create a track of ionization composed of electrons and holes from the semiconductor atoms. The presence of this

Figure 2.5: Illustration of the funnelling effect in a planar transistor [5]

Figure 2.6: SEU in six-transistor (6T) SRAM memory cell [45]

track temporarily distorts the equipotential surfaces of the depletion layer's electric fields. This leads to funnel-shaped equipotential surfaces which can reach into the substrate (see Figure 2.5). Currents of electrons and holes are therefore created, and the deposited charge could be collected by one of the device nodes, resulting in a transient pulse in the circuit. This is especially likely if the particle strikes near the nodes. The amount of charge deposited, and therefore the magnitude of the pulse generated, will depend on the LET of the particle [5].

### 2.4.2 Categorization

#### Single Event Transients

Whenever the charge created by an ionization event discharges through the transistor, a energetic pulse lasting between picoseconds and nanoseconds (depending and pulse width and amplitude) will propagate in the device. This pulse is called a Single Event Transient, and will usually not cause issues in digital devices. If, however, this transient is sampled by a flip-flop, or if it occurs in a memory element, then it becomes a Single Event Upset.

#### Single Event Upsets

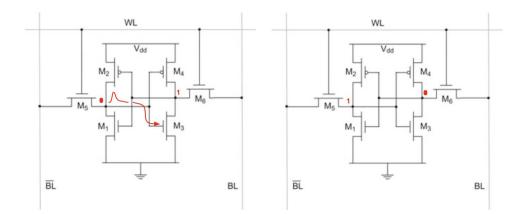

A Single Event Upset (SEU) is any change of state in an electronic device caused by a single particle. As mentioned above, this could be a flip-flop sampling a transient pulse or, as is much more frequent in SRAM-based FPGAs, a bit-flip directly in a memory element. The mechanism by which the value of an SRAM cell is modified by incident radiation is shown on Figure 2.6. In order for a memory element

Figure 2.7: SEU effects in configuration memory. Representing an upset in an LUT module (b) and in the routing matrix (c). [36]

Figure 2.8: Multiple Cell Upsets [54]

to flip, the pulse must have a certain critical charge  $Q_c$ , which has been suggested to be quadratically dependent on feature size L ( $Q_c \propto L^2$ ) [8], although predicting the effects of modern sub-µm scaling on SEU susceptibility is not as straightforward [22]. As this is the main source of concern for radiationinduced soft errors in this thesis, an SEU will from now on be referring to an SEU in memory cells.

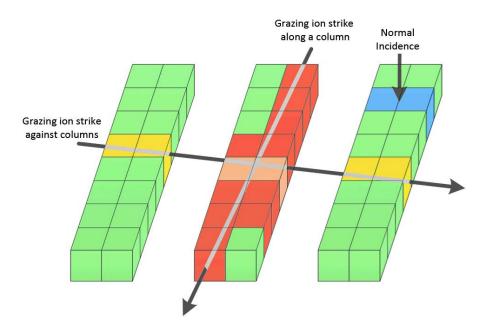

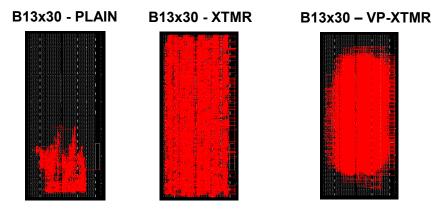

An SEU in the configuration memory of an FPGA will potentially modify the design and can cause any number of issues, the nature of which is difficult to predict (see Figure 2.7). In most firmwares, the number of bits in the bitstream which will change the circuitry is only a fraction of the total bitstream (called *essential bits*)[9], the firmware used in Section 4.3 has an essential bit proportion of about 25%. SEUs can also occur in user memory (e.g. FIFO buffers), which is based around Block RAM (BRAM) in Xilinx FPGAs. Flash and antifuse-based FPGAs are much more resistant to SEUs in their configuration memory, up to total immunity for antifuse FPGAs, but tend to be less performant and both have limitations on their reprogrammability [55].

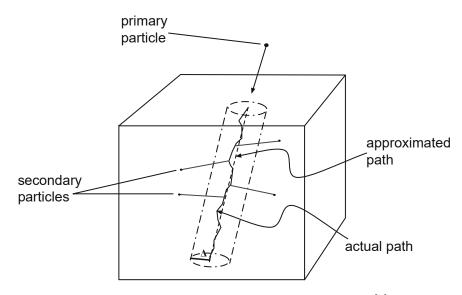

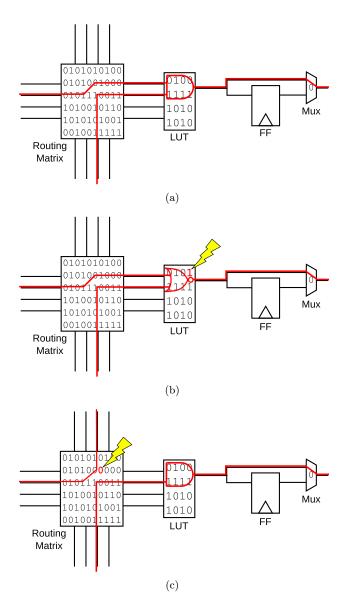

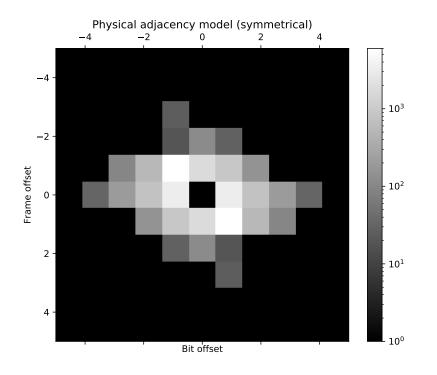

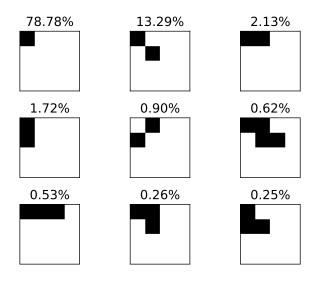

A particle traversing the FPGA can affect multiple memory cells, in that case the SEU is a **Multiple Cell Upset (MCU)**. This can occur when the particle is grazing the device at an angle, or with a normal incidence at the border between memory cells (particles tend to scatter around the silicon rather than follow a linear path), see Figure 2.8. Because a grazing particle is much more likely to go through multiple memory cells, the probability of an MCU will depend on the angle of the device relative to the incident beam of particle. One can also note that the internal layout of an FPGA is such that configuration memory cells are arranged in *columns* (Figure 2.8), therefore one orientation of the angle-of-incidence (along the columns) is much more likely to provoke MCUs than the other (across the columns).

MCUs affecting bits in the same memory frame are a special case, for reasons that will be explained later on, we therefore use a specific term, the **Multiple Bit Upset (MBU)**. If on the other hand the SEU only produces a single bit-flip, then it will be referred to as **Single Bit Upset (SBU)**.

Other sources in the literature might also define SEUs as being single bit upsets (i.e. a 3-bit MCU would count as 3 SEUs), please note that in this thesis an SEU will refer to the **particle event**, which causes one or more memory upsets.

#### Single Event Functional Interrupt (SEFI)

"A soft error that causes the component to reset, lock-up, or otherwise malfunction in a detectable way, but does not require power cycling of the device (off and back on) to restore operability, unlike single-event latch-up (SEL), or result in permanent damage as in single event burnout (SEB)" - JEDEC [15]

A special case of SEU which causes functional problems with the FPGA, but not due to change in the design or user memory. This is often associated with an upset in the control registers of the device.

Figure 2.9: Energy breakdown of neutron radiation in CMS Phase-2 [10]

| Particle          | Possible effects         | Interaction | Prevalence |

|-------------------|--------------------------|-------------|------------|

| Neutron           | Ionization, displacement | High        | High       |

| Electron/Positron | Ionization               | Medium      | Low        |

| Photon            | Ionization               | Low         | Medium     |

| Muon              | Ionization               | Low         | High       |

Table 2.1: Summary of background radiation particles in CMS

Due to the extremely small number of bits existing as control registers, the frequency of SEFI events is usually considered negligible [42].

### Single Event Latchup (SEL)

"An abnormal high-current state in a device caused by the passage of a single energetic particle through sensitive regions of the device structure and resulting in the loss of device functionality. An example of SEL in a CMOS device occurs when the passage of a single particle induces the creation of parasitic bipolar (p-n-p-n) shorting of power to ground. SEL may cause permanent damage to the device. If the device is not permanently damaged, power cycling of the device (off and back on) is necessary to restore normal operation." - JEDEC [15]

Under heavy ion radiation and extreme conditions (above  $90^{\circ}C$  and with supply voltages exceeding maximum specifications), some SEL-like current signatures have been observed in a 7-series Xilinx FPGA [25].

# 2.5 CMS Environment

Now that the most prevalent radiation effects in FPGAs have been presented, we must go back to the CMS to identify which of the background radiation particles will be likely to cause SEUs in the OH FPGA.

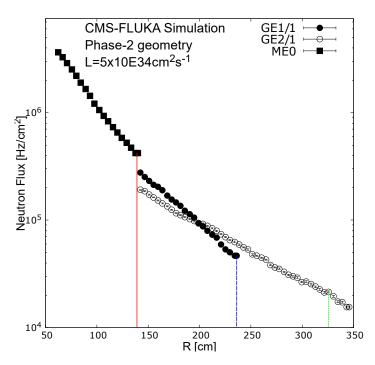

Figure 2.10: Expected neutron flux w.r.t. detector coordinates in CMS Phase-2. Expected flux for ME0 OH, GE1/1 OH, and GE2/1 OH drawn in colour for comparison [10]

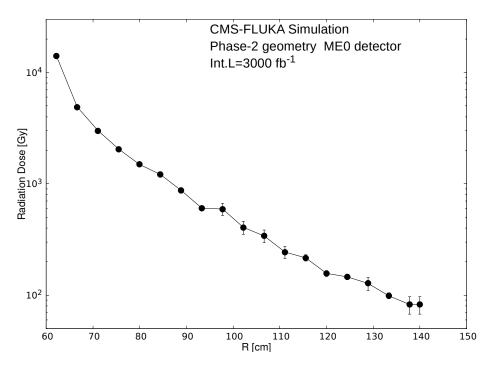

Figure 2.11: Expected TID w.r.t. detector coordinates in CMS Phase-2 [10]

Figure 2.12: CRAM proton cross-section data related to proton energy for the Virtex-6 [29]

The CMS background radiation is mainly composed of neutrons, electrons (and positrons), photons and muons. The dominant source of SEUs will be neutrons. Muons do not have a significant impact on SRAM memory cells [51], they will therefore not influence the SEU rate. The combined flux of electron and positrons is over two orders of magnitude lower than neutrons, and the electron cross-section at the CMS energy levels is two order of magnitudes lower than the neutrons'. Photons have a similar flux but will not interact with the silicon of the FPGA [29]. Table 2.1 summarizes the effects and prevalence of the principal background radiation particles in CMS.

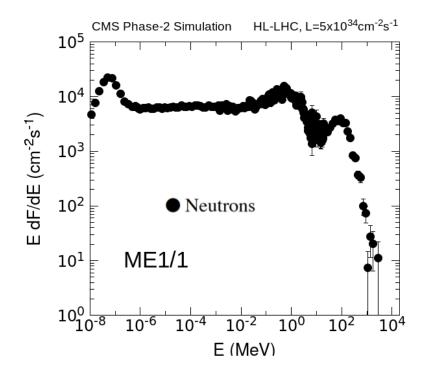

The Technical Design Report for the Phase-2 Upgrade of the CMS detector contains information on the environmental radiation [10]. These values were obtained through complex computer simulations of the CMS detector and cavern after a beam crossing, including among other things the neutrons produced by the hadronic showers in the detector. Figure 2.9 contains the expected neutron energy distribution in the detector. This can be used along with an energy-related SEU cross-section (e.g. CRAM, BRAM) to predict an effective SEU rate in CMS. Figure 2.10 shows the expected neutron flux for various elements depending on their position within CMS coordinates, one can see from this graph that an approximate increase of one order of magnitude in the neutron flux is to be expected for ME0 relative to GE1/1 (the OH location on the detector board will be the furthest away from the center of the CMS, around R = 150 cm, see Figure 1.5). This would be in the  $10^5$  Hz cm<sup>-2</sup> range. The neutron flux expected for GE2/1 is comparable to the GE1/1 levels, in the  $10^4$  Hz cm<sup>-2</sup> range. Finally the Total Ionizing Dose (TID) for the ME0 OptoHybrid is estimated at around 30 krad (Figure 2.11). As both the ME0 and G2/1 use the same Artix-7 FPGA, it is sufficient to qualify the board for the highest radiation level at the ME0 location.

An additional consideration is that the proportion of MCUs among SEUs is related to the tilt of the beam relative to the surface of the FPGA [26] (see Section 5.1.2). In the case of the ME0 detector, the incident angle relative to the interaction point is  $\approx 15^{\circ}$ , but in the CMS cavern, particles can be expected from all direction. Simulation data on the probability distribution of the particle angle-ofincidence would therefore be useful to give accurate predictions on the proportion of MCUs and MBUs, however this is not currently available.

### 2.6 Existing studies

### GE1/1

Previous studies on the radiation resistance of the OptoHybrid board's FPGA were done at the Inter University Institute For High Energies (Brussels) in 2016 for the GE1/1 detector [28] [29], which used a Virtex-6 FPGA. The tests were conducted at the UCLouvain's Cyclone particle accelerator, using a beam of protons (which have an interaction cross-section very similar to neutrons [52]). The results obtained by T. Lenzi are reproduced on Figures 2.12 and 2.13. The SEM data refers to the SEU detection events reported by the SEM IP Core (see Section 3.2.5). The number of SEUs per day is extrapolated from the expected flux at GE1/1, the neutron energy distribution, and the cross-section data related to proton energy shown on Figure 2.12. One can observe that the cross-section reduces greatly at 20MeV.

| Event type         | cross section                        | SEUs per day<br>LHC Phase I | SEUs per day<br>LHC Phase II |

|--------------------|--------------------------------------|-----------------------------|------------------------------|

| SEM - recoverable  | $3.08 \times 10^{-7}  \mathrm{cm}^2$ | 13.3                        | 33.2                         |

| SEM - critical     | $3.19 \times 10^{-8}  \mathrm{cm}^2$ | 1.36                        | 3.44                         |

| BRAM - recoverable | $1.02 \times 10^{-7}  \mathrm{cm}^2$ | 4.38                        | 11                           |

| BRAM - critical    | $1.71 \times 10^{-8}  \mathrm{cm}^2$ | 0.54                        | 1.33                         |

| CLB                | $2.88 \times 10^{-7}  \mathrm{cm}^2$ | 12.42                       | 31                           |

| DSP                | $2.04 	imes 10^{-8}  \mathrm{cm}^2$  | 0.88                        | 2.2                          |

Figure 2.13: Proton cross-section data for the Virtex-6 [29]

| Energy          | $\sigma_{upset}$ per device            | $\sigma_{upset}$ normalized by CRAM size                  |

|-----------------|----------------------------------------|-----------------------------------------------------------|

| $35 { m MeV}$   | $15 \times 10^{-8} \mathrm{cm}^{-2}$   | $7.94 \times 10^{-15} \mathrm{cm}^{-2} \mathrm{bit}^{-1}$ |

| $100 { m MeV}$  | $10 \times 10^{-8}  \mathrm{cm}^{-2}$  | $5.3 \times 10^{-15} \mathrm{cm}^{-2} \mathrm{bit}^{-1}$  |

| $200~{\rm MeV}$ | $6.75 \times 10^{-8} \mathrm{cm}^{-2}$ | $3.57 \times 10^{-15} \mathrm{cm}^{-2} \mathrm{bit}^{-1}$ |

Table 2.2: Cross-section data for the Kintex-7 [33]

It should be noted that cross-section results, and the calculated time between upsets is based on the total number of bits in the configuration memory. Of those bits, only a fraction (the exact value depends on the firmware) are actually essential to the functionality of the design. Should a non-essential bit be affected, the design will not change.

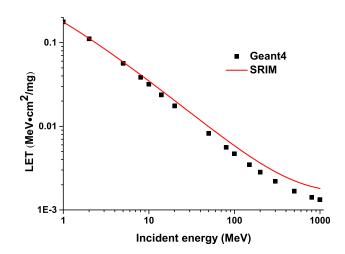

### **CRAM SEU** cross-section

Xilinx provides some neutron cross-section data for all their FPGA families in the "Device Reliability" Report", though the Los Alamos Neutron Science Center (LANSCE) facility where their tests were run is a wide-spectrum neutron beam, therefore there are no cross-section values for specific energy levels. At the time of the preliminary research for this thesis, besides the Xilinx report, no specific irradiation data for the Artix-7 FPGA was found, however several studies had been made on the Kintex-7 FPGA, which has a very similar architecture [1]. The results obtained by one of those studies is reproduced in Table 2.2. The cross-section results are normalized by CRAM size, as a larger FPGA (i.e. with more logic cells) will evidently have more errors than a smaller one with the same density. Comparing the trends in Figure 2.12 and Table 2.2, we can see that in one case the cross-section rises with energy, and in the other it falls with energy. The latter could be explained by the fact that higher energy protons (and neutrons), which can travel further into the silicon, actually have a lower LET (see Figure 2.15) [19]. The former may be occurring because the energy of the incident protons falls below the threshold of the nuclear reactions required for ionization of the silicon [7]. This explanation may be somewhat simplistic, however going into further detail would require a more in-depth approach to neutron interactions in the silicon lattice, which is outside the scope of this chapter. It is sufficient for our purposes to note that this behaviour has been observed in other SEE studies [7].

These results can be compared to the Xilinx data, reproduced in Figure 2.14. It can be seen that the Artix-7 and Kintex-7 cross-sections are close, but slightly higher for the Artix-7. The Kintex-7 results from Xilinx were also independently verified by a research group at the NSF Center for High Performance Reconfigurable Computing [56].

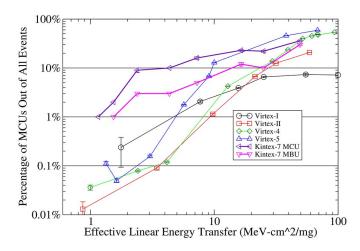

### MCU proportion

Existing data already shows that LET and angle of incidence have a large impact on the proportion of MCUs in Kintex-7 FPGAs [26] [57]. There is no reason to think the same should not expected for the Artix-7. At normal incidence, the proportion of MCU in the Kintex-7 was measured at  $\approx 10\%$  for intra-frame MBUs, and  $\approx 35\%$  for all MCUs [56] at the LANSCE wide-spectrum neutron beam.

#### TID

Concerning the TID, previous irradiation campaigns on the Kintex-7 have reached values of 500krad [33], and even 1 Mrad [34], without permanent damage to the device. This is much higher than the 30krad

| Tech Node | Product<br>Family                          | LANSCE Neutron<br>Cross-section per Bit <sup>(2)</sup> |       | FIT/Mb<br>(Thermal<br>Neutrons) |                        | FIT/Mb<br>(Alpha Particle) <sup>(3)</sup> |                        | FIT/Mb <sup>(4)</sup><br>(Real-Time Soft<br>Error Rate Per<br>Event) <sup>(5)(7)</sup> |                        |

|-----------|--------------------------------------------|--------------------------------------------------------|-------|---------------------------------|------------------------|-------------------------------------------|------------------------|----------------------------------------------------------------------------------------|------------------------|

|           |                                            | CRAM                                                   | Error | CRAM                            | Error <mark>(6)</mark> | CRAM                                      | Error <mark>(6)</mark> | CRAM                                                                                   | Error <mark>(6)</mark> |

| 180 nm    | Virtex-E                                   | 1.12 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 181                                                                                    | ±20%                   |

| 150 nm    | Virtex-II                                  | 2.56 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 405                                                                                    | ±8%                    |

| 130 nm    | Virtex-II Pro                              | 2.74 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 437                                                                                    | ±8%                    |

| 90 nm     | Virtex-4                                   | 1.55 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 263                                                                                    | ±11%                   |

| 90 nm     | Spartan-3                                  | 2.40 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 190                                                                                    | -50%<br>+80%           |

| 90 nm     | Spartan-3E,<br>Spartan-3A                  | 1.31 x 10 <sup>-14</sup>                               | ±18%  |                                 |                        |                                           |                        | 104                                                                                    | -80%<br>+90%           |

| 65 nm     | Virtex-5                                   | 6.70 x 10 <sup>-15</sup>                               | ±18%  |                                 |                        |                                           |                        | 165                                                                                    | -13%<br>+15%           |

| 45 nm     | Spartan-6                                  | 1.00 x 10 <sup>-14</sup>                               | ±18%  | 21                              | –11%<br>+13%           | 88                                        | -50%<br>+100%          | 177                                                                                    | -10%<br>+11%           |

| 40 nm     | Virtex-6                                   | 1.26 x 10 <sup>-14</sup>                               | ±18%  | 0.7                             | –11%<br>+13%           | 7                                         | -45%<br>+97%           | 105                                                                                    | -10%<br>+11%           |

| 28 nm     | Artix-7,<br>Spartan-7,<br>and<br>Zynq-7000 | 6.99 x 10 <sup>-15</sup>                               | ±18%  | 29                              | -10%<br>+10%           | 43                                        | -41%<br>+80%           | 75                                                                                     | -9%<br>+10%            |

| 28 nm     | Kintex-7 and<br>Virtex-7                   | 5.69 x 10 <sup>-15</sup>                               | ±18%  | 1.1                             | –15%<br>+18%           | 43                                        | -41%<br>+80%           | 67                                                                                     | -24%<br>+34%           |

| 20 nm     | UltraScale                                 | 2.55 x 10 <sup>-15</sup>                               | ±18%  | 0.5                             | -13%<br>+16%           | 9                                         | -64%<br>+374%          | 30                                                                                     | -16%<br>+19%           |

| 16 nm     | UltraScale+                                | 2.67 x 10 <sup>-16</sup>                               | ±18%  | 0.35                            | -16%<br>+20%           | 0.1                                       | -20%<br>+20%           | 6                                                                                      | -28%<br>+42%           |

Figure 2.14: Xilinx configuration memory cross-section data [14]

Figure 2.15: Simulated proton LET in silicon [19]

| Family   | Device  | Logic cells | BRAM (Max Kb) | Bitstream length (bits) |

|----------|---------|-------------|---------------|-------------------------|

| Virtex-6 | VSX315T | 314,880     | 25,344        | 104,465,888             |

| Virtex-7 | VX330T  | 326,400     | 27,000        | 111,238,240             |

Table 2.3: Comparison of two FPGAs with similar logic capabilities across two families.

Figure 2.16: MCU proportion out of all events, related to heavy ion LET and device family [57]

expected over the lifetime of the ME0 detector, therefore no significant accumulated effects are expected for the Artix-7.

## 2.6.1 Scaling trends

### SEU cross-section

Looking at the historical cross-section data in Figure 2.14, it can be seen that the SEU rates per CRAM bit are going down with shrinking technology nodes, which seems counter-intuitive. Xilinx reports that this as been achieved through improvements in circuit design and layout techniques. By comparing two models in the Virtex-6 and Virtex-7 families with a similar amount of logic elements (see Table 2.3) we can see that the bitstream length (i.e. the number of configuration bits in the FPGA) remains stable. This seems to indicate that some technological improvement towards radiation hardening was indeed made in the circuit design.

As technology nodes go beyond 20nm, FinFET architectures can be expected to replace the current planar devices. Indeed, the high-end Xilinx Ultrascale+ family is now built on a 16nm FinFET process. Interestingly, experimental data seems to indicate that, when compared to 20nm and 28nm planar devices, the SEU cross-section is lower at low LETs ( $< 10 \text{ MeV cm}^2 \text{ mg}^{-1}$ ), while staying stable at higher LETs [32]. From the Xilinx data we can see an order of magnitude reduction in SEUs for the 16nm FinFET Ultrascale+ when compared to the planar 20nm Ultrascale, with the LANSCE neutron beam.

### MCU proportion

Although the SEU cross-section may improve in new technology nodes, the proportion of MCUs in planar devices is unmistakingly increasing, see Figure 2.16 (note the logarithmic scale). As for FinFET devices however, preliminary testing on the Ultrascale+ family with heavy ions reveals a significantly reduced MCU response relative to the Kintex-7 at  $\approx 7\%$  in the 20 MeV cm<sup>2</sup> mg<sup>-1</sup> region [27]. As we shall see in the next chapter, MBUs are quite problematic in simple SEU mitigation schemes.

# Chapter 3

# SEU mitigation techniques

# 3.1 Radiation hardening solutions

Radiation hardening is the process of making an electronic device/system resistant to damage or malfunctions caused by radiation. The means by which radiation can affect an FPGA have been presented in the previous chapter. As it was established that accumulated effects would not be a problem in the context of CMS, we will focus on solutions to single-event effects. In particular, we will focus on mitigating the effects of single event upsets in the configuration memory.

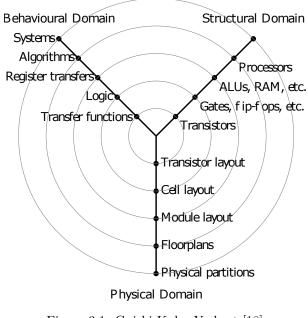

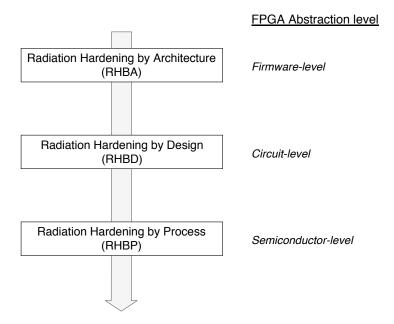

Just as there are multiple levels of abstraction for VLSI design (Figure 3.1), there are multiple levels of abstraction for radiation hardening depending on when it is applied in the development of an electronic device. Figure 3.2 illustrates the 3 types of radiation hardening and relates them to FPGA-appropriate abstraction levels.

The lowest level solution is Radiation Hardening by Process (RHBP), where the transistors of the electronic devices have been fabricated with semiconductor process technologies which temper the component against the effects of incident particles. This can involve specific material selection, insulation layers (e.g. Silicon-On-Insulator devices are immune to single event latch-up [30]), doping levels, and others. This is an expensive solution, which relies on dedicated foundries. Because of this, and the small size of the market, RHBP electronics tend to lag behind commercial-off-the-shelf (COTS) equipment by a decade or more [23].

Radiation Hardening By Design (RHBD) is the next level over, it implies that the electronic device or component has been radiation-hardened by specific choices in layout and circuit architecture. Examples of RHBD include increased component spacing, isolation trenches in the chip layout, component redundancies built into the circuit, and the memory frame interleaving scheme in Xilinx FPGAs (see Section 3.2.5). Although these methods can be applied with normal manufacturing processes, there is a trade-off being made with other device characteristics, be it in integration density (e.g. component spacing), power consumption (e.g. redundancies) or cost, to name a few. For these reasons, mainstream COTS devices will only include a limited amount of RHBD features at best.

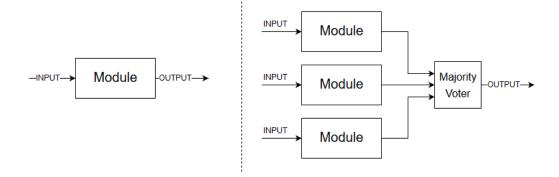

Finally, Radiation Hardening by Architecture (RHBA) includes all techniques which can be applied when integrating non-hardened components into the final system/device. In an ASIC (Application-Specific Integrated Device), this could be adding redundancy by duplicating a non-hardened standard cell. For an FPGA, this will principally be schemes applied in the firmware. At the firmware level, the standard scheme for SEU mitigation in the configuration memory of an FPGA is done by combining two complementary techniques: **Memory scrubbing** and **N-Modular redundancy**. Scrubbing means going through the memory and iteratively repairing damaged sections. This of course requires some sort of data redundancy, either in the form of error-correction codes (ECC), or access to a clean version of the firmware. Modular redundancy is a way to mask the effects of an SEU in the CRAM, until the scrubbing can repair it. The principle is simple, duplicate the firmware module which requires protection N-times, and add a majority voter at the output. The devil, though, is in the details.

Figure 3.1: Gajski-Kuhn Y chart [18]

Figure 3.2: Radiation hardening types, related to the abstraction level of an FPGA

# 3.2 Scrubbing architectures

## 3.2.1 Blind scrubbing

The simplest approach to memory scrubbing is to systematically rewrite every frame of memory. This is called blind scrubbing as no attempt is made to verify the content of the memory before rewriting it. This approach requires the use of a **golden copy**, a copy of the firmware known to be correct, stored in an accessible location (e.g. a rad-hard memory near the FPGA, or a low latency off-detector copy).

The total scrubbing time for blind scrubbing is

$$T_{s_{blind}} = N \cdot T_c \tag{3.1}$$

where N is the number of frames in the CRAM and  $T_c$  is the latency of one write operation to a CRAM frame [47]. It may be desirable to add delays to the write operations to ease processing bandwidth resources, in this case then

$$T_{s_{blind}} = N \cdot (T_c + T_{delay}) \tag{3.2}$$

| Advantages                                           | Disadvantages                   |

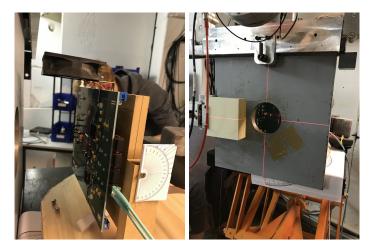

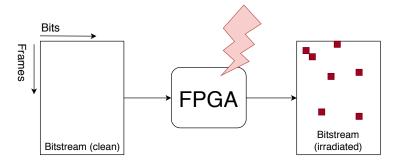

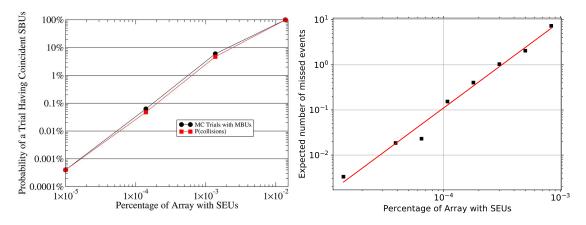

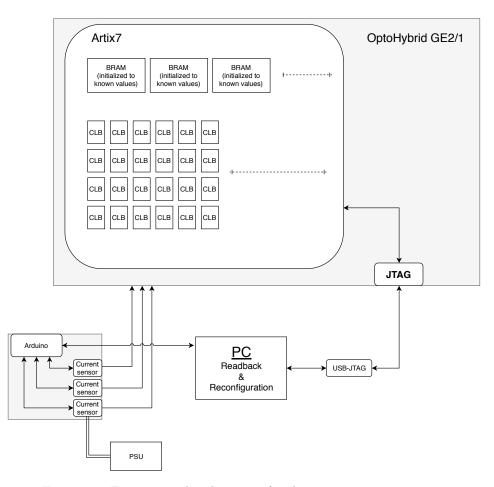

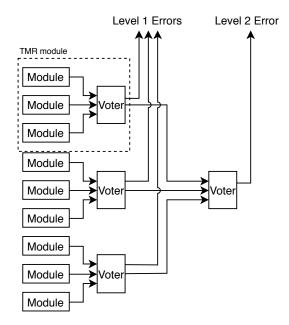

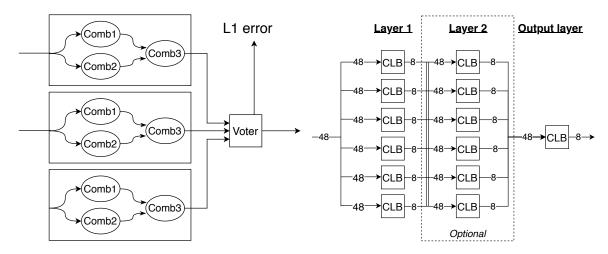

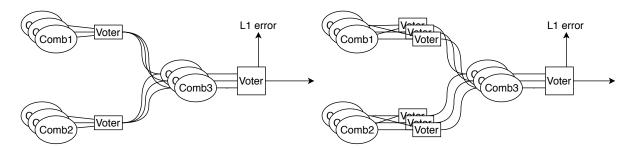

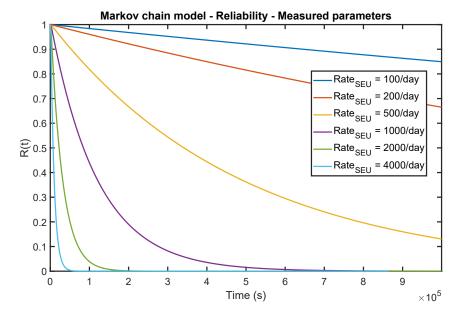

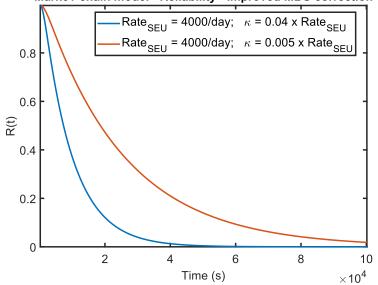

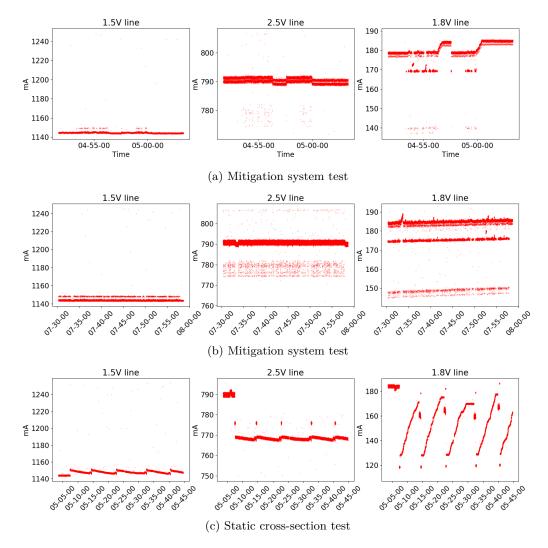

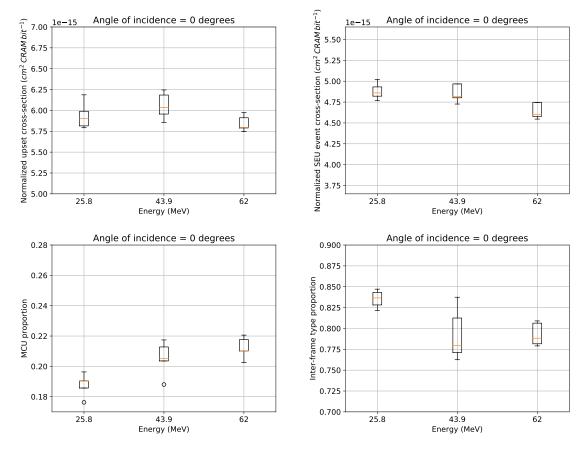

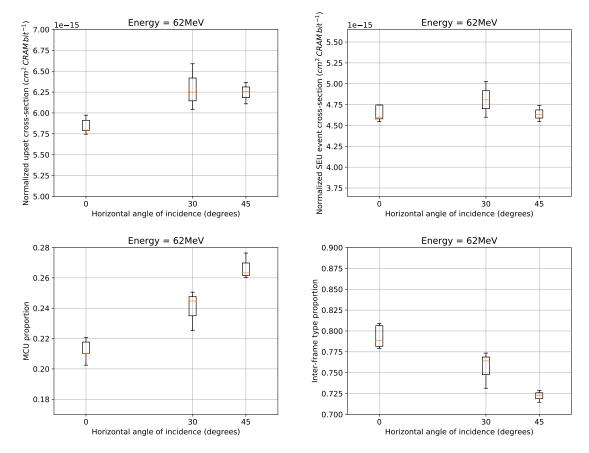

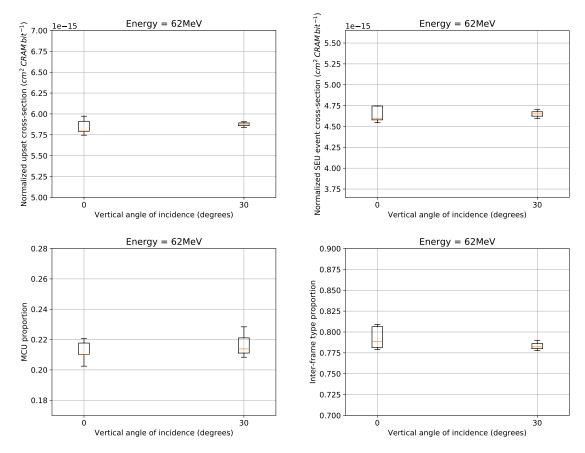

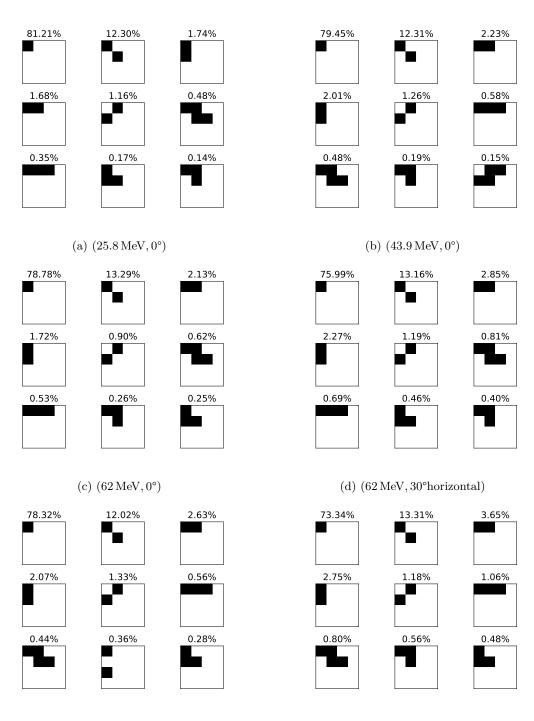

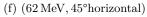

|------------------------------------------------------|---------------------------------|